## Development of a Geographically Distributed Real-Time Test Facility

## ENGAGED WIND Project PNDC & OREC test platform

- 1. Multi-site overview, project summary and objectives

- 2. Experimental setup review: RTDS model & Opal-RT model & communication link

- 3. Final model for Stage 1

- 4. Results

- 5. Scenario study overview: Defined from stakeholder engagement

- 6. Next steps: Stage 2 project

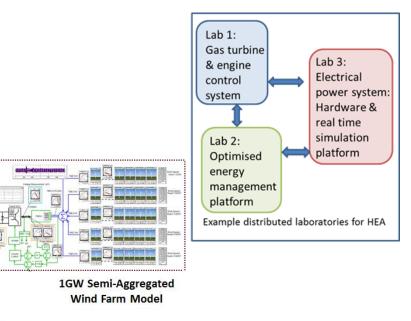

## What and why: Multi-site hardware in the loop?

6 Machine Reduced Equivalent Model of GB

- Comprehensive characterization and effective demonstration (linking facility and expertise)

- Representative system studies >> Realism

- Large system studies >> Scalability

- Detailed system studies >> Fidelity

**MVDC Grid**

## **Project Summary**

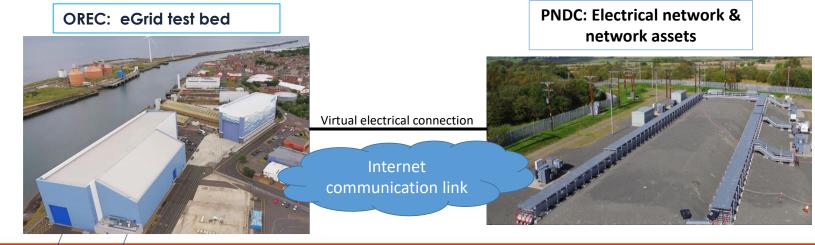

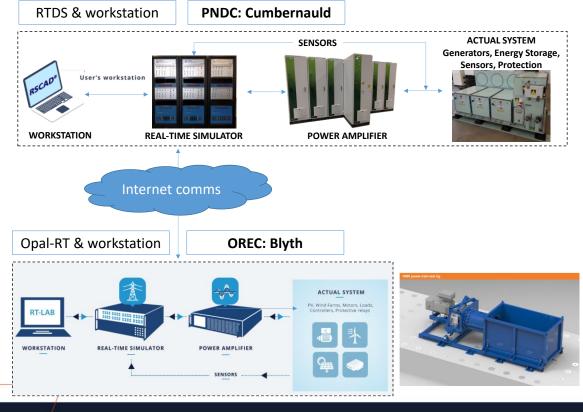

- Long term vision realise the potential for using Power Hardware in the Loop techniques to link the geographically distributed Power Networks Demonstration Centre (PNDC), Dynamic Power Systems Lab (DPSL), and OREC's drivetrain and eGrid test facilities.

- **Project Value** This multi-site setup will enable several valuable test options, primarily it will allow expanded **system level testing** that would not be possible at one of the single test sites in isolation.

## **Project Objectives**

- Opportunity shaping and scenario building for distributed (multi-site) power and control testing capability (including key stakeholder engagement)

- 2. Development of experimentation plan, distributed laboratory configuration, commissioning experiment and analysis.

- 3. Business case assessment and testing specification for resilient performance assessment and the evaluation of regulation and policy requirements.

- 4. Use-case focused experiment for demonstration of capability.

- 5. Recommendations for future research investigations and commercial testing.

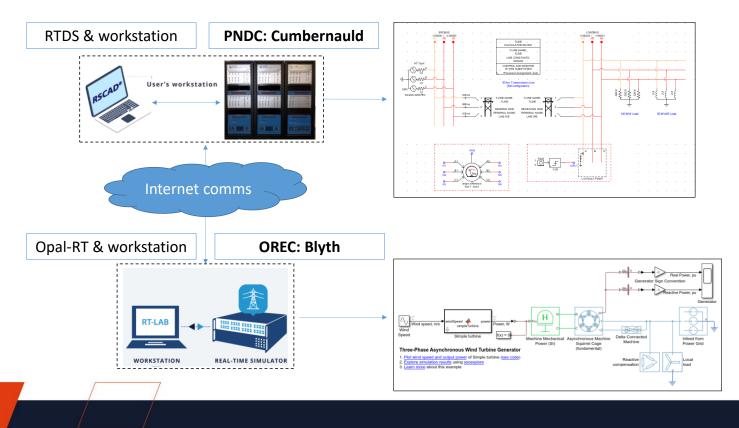

## Experimental Setup: Models

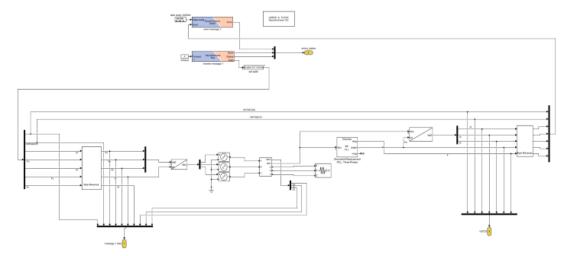

## Initial Experimental Setup: RTDS Model

UDP Comms Interface

Currents Rec

- Decomposition of Voltage to OPAL-RT to d/q/ph

- Reconstruction of Current from OPAL-RT

- Calculation of Time Delay and compensation

- Controlled Voltage Source

- Current Sources as Inputs

- Next step, replacing VS with GB network

## Initial Experimental Setup: Opal-RT Model

- UDP Comms Interface

- Reconstruction of Voltage from RTDS

- Decomposition of Current to RTDS d/q/ph

- Voltage sources as Input

- Load

.

• Next step replacing the Load with WF

## Experimental Setup: Communications testing

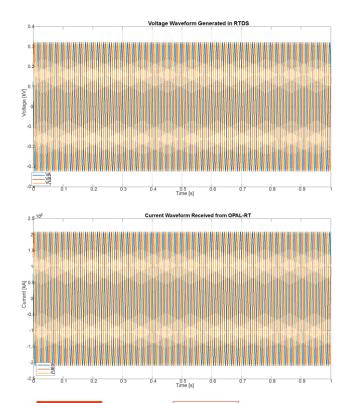

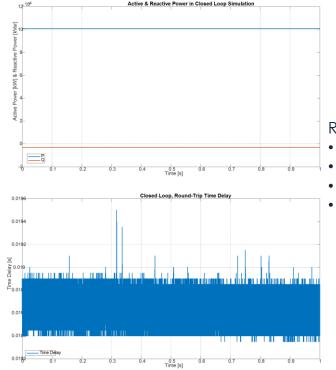

#### Results from first iteration

- V = 325V

- I=2A

- P=1000W

- Time Delay = 18ms

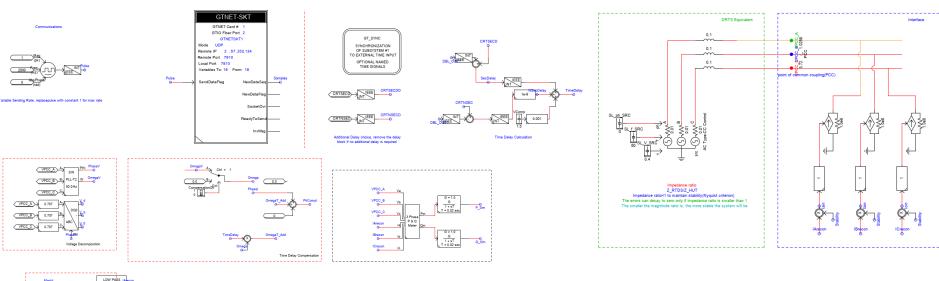

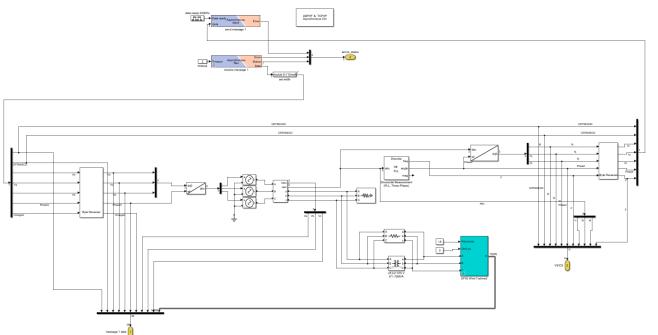

## Finalized Experimental Setup: RTDS Model

#### Electrical Elements & Data

- 6 x 1.6MW DFIG WT

- 1 x 400kV/575V Transformer

## Finalized Experimental Setup: RTDS Model

#### Traparty F.D.C.S. BUSB \* (Tru) G T+ aT mag BUSSC and that G 1 + aT PI SECTION Name - P12 (hu) G Ta + Figs BUSD of the DC g -Traparty of Junior G Trat Trat Dutie PI SECTION CORE IN LOOP Midde of English CEBUSUNCE. BUSLINK2 o BUSF BUSH FESC Ent /Q Ent PI SECTION PI SECTION iane - Pie SECTION 000101400 BUSHINK' G 8 8

#### Electrical Elements & Data

- 5 Bus GB distribution

- 66GVA

- •

Finalized Experimental Setup: Frequency Event

## Phase 2 project ambition

## Scenario for testing

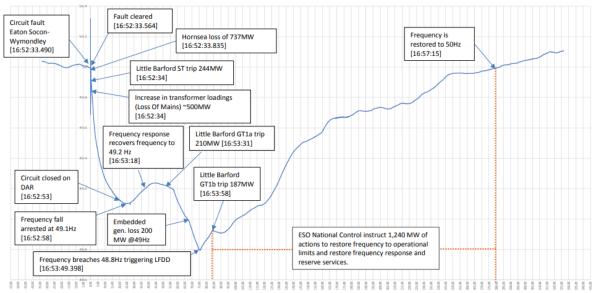

Developed following on from feedback from the workshop event and follow on industry engagement.

Simulation scenario based on 9<sup>th</sup> August 2019 event: **Frequency Deviation**

# Thank you

Kyle Jennett Lead R&D Engineer kyle.jennett@strath.ac.uk

Michael Smailes Senior Research Engineer, Grid Integration <u>michael.smailes@ore.catapult.org.uk</u>

Mazheruddin Syed Research Fellow <u>mazheruddin.syed@strath.ac.uk</u>

Andreas Avras Smart Grid Research Engineer <u>a.avras@strath.ac.uk</u>