Fulfilment of grid code obligations by large offshore wind farms clusters connected via HVDC corridors

#### EERA DeepWind'2016

A. B. Attya\* O. Anaya-Lara P. Ledesma H. G. Svendsen

\*presenter<sup>:</sup> Wind Energy Research Group

University of Strathclyde

Presented research is conducted in the frame of EERA-DTOC project

January 14, 2016 | Electronics and Electrical Engineering | Ayman B. Attya |

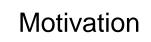

#### Motivation

- Grid code and ancillary services

- Implementation challenges

- Benchmark system and case studies

- Results

- Conclusions

## EERA DeepWind'2016

### Motivation

- High penetration levels of wind power imposes its contribution to voltage stability

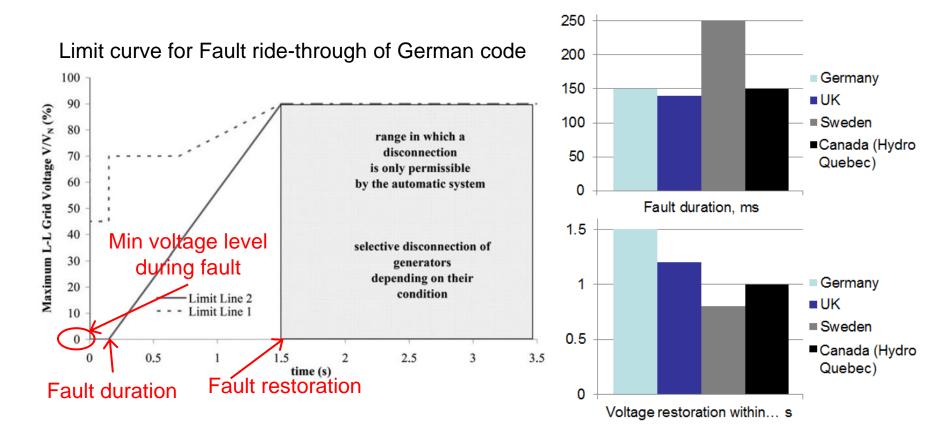

- Solving challenges of the utilization of Net-OP tool results to prepare a highly detailed dynamic model using PSS®E

- Investigate the influence of HVDC links connecting the wind farms clusters

Grid code and ancillary services

- Implementation challenges

- Benchmark system and case studies

- Results

- Conclusions

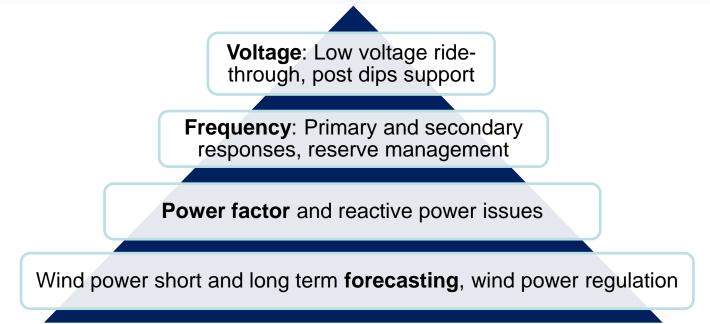

### Grid code and ancillary services

Grid Code specifies the technical requirements and obligations on the connection to, and utilization of, certain transmission system(s). This system could be national or international (e.g. unified European grid)

Ancillary services provided by power plants and Grid Code requirements are two sides of one coin

### Grid code and ancillary services

M. Tsili and S. Papathanassiou, "A review of grid code technical requirements for wind farms," *Renewable Power Generation*, vol. 3, 2009

- Grid code and ancillary services

- Implementation challenges

- Benchmark system and case studies

- Results

- Conclusions

January 14, 2016 | Electronic and Electrical Engineering | Ayman B. Attya |

## **Implementation challenges**

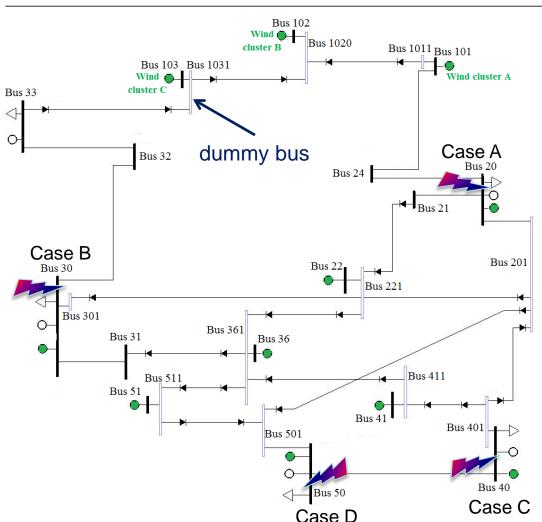

- In PSS®E, swing bus could not be connected to a DC link → a dummy bus is added to connect the main bus to the DC link(s)

- Setting the rated voltage and power capacities of DC links

- Net-OP does not provide a \*.DYR file, thus dynamic models are assigned to all system components from scratch

- Integrating controllers' types of HVDC links (assumed as CDCT4)

- Motivation

- Grid code and ancillary services

- Implementation challenges

- Benchmark system and case studies

- Results

- Conclusions

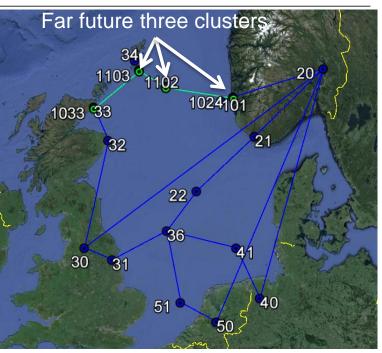

### **Benchmark system and case studies**

**EERA DeepWind'2016**

University of Strathclyde

All faults are **3-phase** symmetrical and cleared after **120 ms**

- Motivation

- Grid code and ancillary services

- Implementation challenges

- Benchmark system and case studies Results

- Conclusions

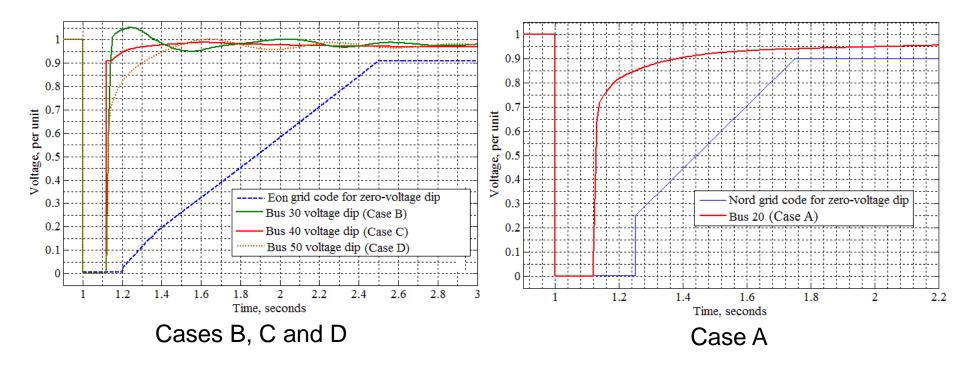

# Results— voltage response compared to grid code

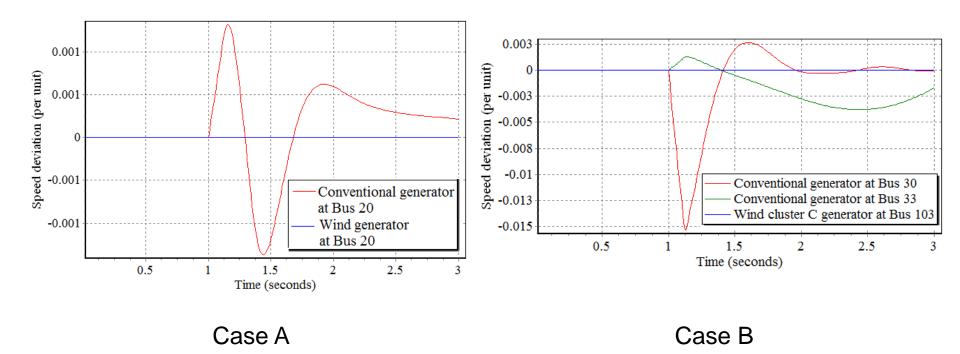

## Results— response of generators' speeds

**EERA DeepWind'2016**

University of Strathclyde

Engineering

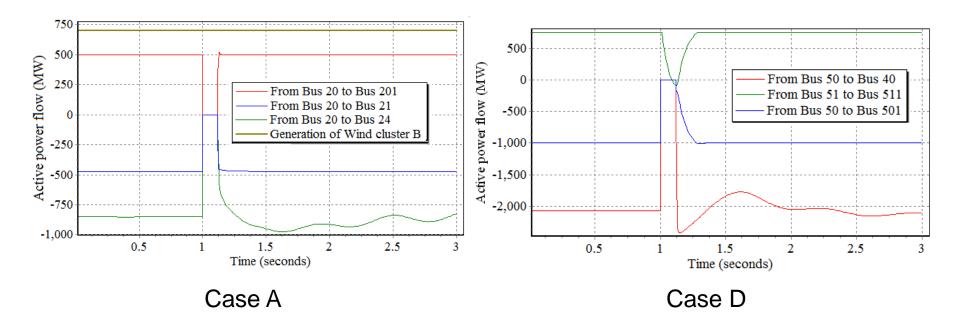

## **Results— samples for power flow variations**

#### Motivation

- Grid code and ancillary services

- Implementation challenges

- Benchmark system and case studies

- Results

- Conclusions

## Conclusions

- The integration of far future wind clusters does not violate the grid codes during voltage dips

- HVDC failed in some cases to provide the required reactive current to the nearby faulted bus because the converters' models in PSS®E are not equipped with the suitable control methods

- Efforts are required to obtain the real (i.e. generic) values for all the parameters applied in the PSS®E model

- Industrial parties are encouraged to publish samples from real data of related components (e.g. HVDC links converters)

- Comprehensive efforts are required to design new grid codes which specify clearly the role of HVDC links in providing ancillary services

### Thanks for your attention

January 14, 2016 | Electronic and Electrical Engineering | Ayman B. Attya |

# Appendix— numerical values of the parameters of HVDC controllers

Strathclyde Engineering

| VSCDCT                                                                                                     |      |                                                                                                           |      |

|------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------|------|

| J Tpo_1, Time constant of active power order controller, sec (VSC # 1).                                    | 0.05 | J+14 AC_VC_Limits_2, Reactive power limit for ac voltage control, pu on converter MVA rating              | 0    |

| J+1 AC_VC_Limits_1, Reactive power limit for ac voltage control, pu on converter MVA rating                | 0    | J+15 AC_Vctrl_kp_2, AC Voltage control proportional gain, converter MVA rating/BASEKV (VSC#2).            | 2.4  |

| J+2 AC_Vctrl_kp_1, AC Voltage control proportional gain, converter MVA rating/BASEKV (VSC # 1).            | 2.4  | J+16 Tac_2 > 0.0, Time constant for AC voltage PI integral, sec (VSC#2). When 0, VSC#2 is ignored.        | 0.01 |

| J+3 Tac_1 > 0, Time constant for AC voltage PI integral, sec (VSC#1).                                      | 0.01 | J+17 Tacm_2, Time constant of the ac voltage transducer, sec (VSC#2), must be longer than simulation step | 0.05 |

| J+4 Tacm_1, Time constant of the ac voltage transducer, sec (VSC # 1), must be longer than simulation step | 0.05 | J+18 lacmax_2, Current Limit, pu on converter MVA rating (VSC#2).                                         | 1    |

| J+5 lacmax_1, Current Limit, pu on converter MVA rating (VSC#1).                                           | 1    | J+19 Droop_2, AC Voltage control droop, converter MVA rating/BASEKV (VSC#2).                              | 0    |

| J+6 Droop_1, AC Voltage control droop, converter MVA rating/BASEKV (VSC#1).                                | 0    | J+20 VCMX_2, Max. VSC Bridge Internal Voltage (VSC#2).                                                    | 1.07 |

| J+7 VCMX_1, Max. VSC Bridge Internal Voltage (VSC#1).                                                      | 1.07 | J+21 XREACT_2 > 0.0, Pu reactance of the ac series reactor on converter MVA rating (VSC# 2)               | 0.17 |

| J+8 XREACT_1 > 0.0, Pu reactance of the ac series reactor on converter MVA rating (VSC#1).                 | 0.17 | J+22 QMAX_2, Max. system reactive limit in MVAR (VSC#2).                                                  | 240  |

| J+9 QMAX_1, Max. system reactive limits in MVAR (VSC#1)                                                    | 240  | J+23 QMIN_2, Min. system reactive limits in MVAR (VSC#2).                                                 | -740 |

| J+10 QMIN_1, Min. system reactive limits in MVAR (VSC#1).                                                  | -740 | J+24 AC_VC_KT_2, feedback from reactive power limiter to ac voltage controller (VSC#2)                    | 1.2  |

| J+11 AC_VC_KT_1, feedback from reactive power limiter to ac voltage controller (VSC#1).                    | 1.2  | J+25 AC_VC_KTP_2, feedback from current order limiter to ac voltage controller (VSC#2).                   | 1    |

| J+12 AC_VC_KTP_1, feedback from current order limiter to ac voltage controller (VSC#1).                    | 1    | J+26 Tpo_DCL, Time constant of the power order controller, sec (DC Line).                                 | 0.05 |

| J+13 Tpo_2, Time constant of active power order controller, sec (VSC#2).                                   | 0.05 | J+27 Tpo_lim, Time constant of the power order limit controller, sec (DC Line).                           | 0.05 |

January 14, 2016 | Electronic and Electrical Engineering | Ayman B. Attya |